PROMISE Pilot Circuit CDR Milestone Successfully Reached

PROMISE consortium announces the achievement of CDR completion for the PROMISE Pilot Circuit on 31st of January 2023.

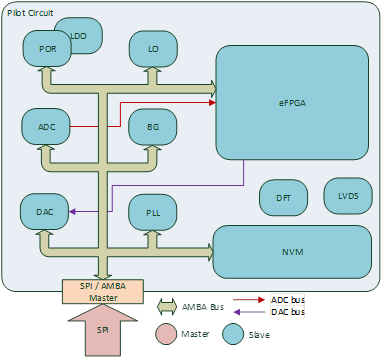

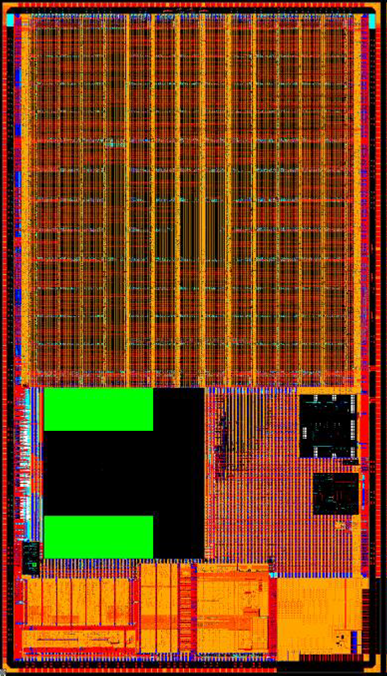

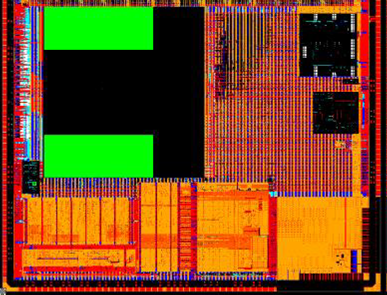

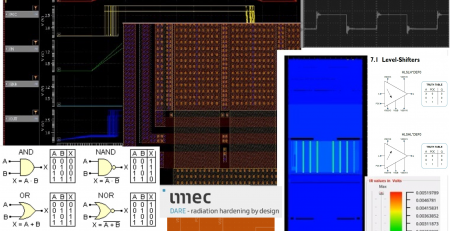

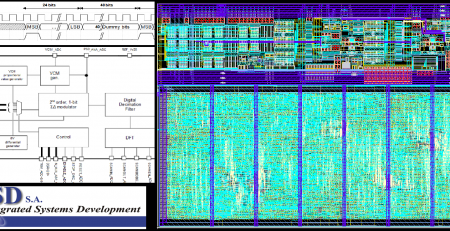

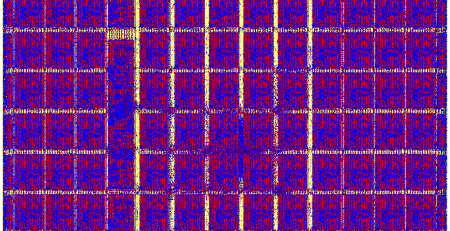

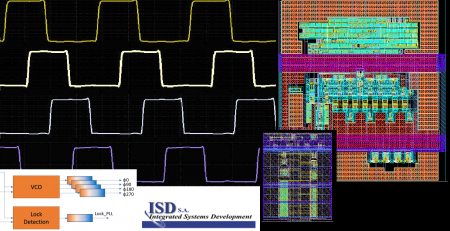

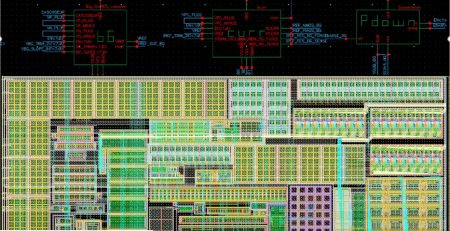

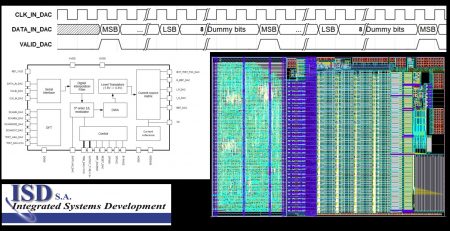

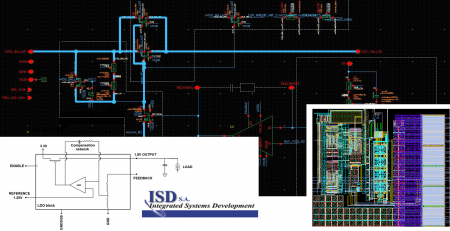

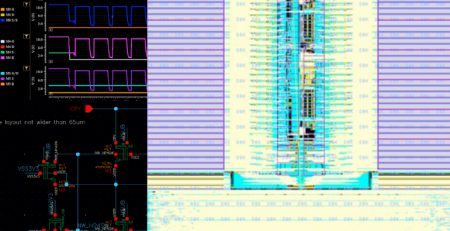

The circuit embeds all IPs designed by the partners : Power-On-Reset (designed by VTT), Low-Drop-Out, Analog-to-Digital-Converter, Digital-to-Analog-Converter, Phase-Locked-Loop (designed by ISD), Bandgap reference voltage, Local Oscillator (designed by IT), embedded FPGA (designed by MENTA), Non-Volatile-Memory, LVDS (designed by IMEC). IPs are connected at the digital top level based on the DARE180X hardened library. All PROMISE Pilot Circuit verification by simulation and physical implementation have been made using the data-package delivered for each IP : circuit front-end design has been performed by TAS-France and circuit back-end design by IMEC. The circuit has 352 pins and is 11mm x 19mm size. The PROMISE Pilot Circuit architecture allows to access all IPs individually for characterization and offers capabilities to operate signals from ADC to eFPGA, eFPGA to DAC whereas eFPGA bitstream can be loaded from NVM, from SPI or from primary pins. The NVM can be R/W through primary pins or SPI.

Pilot Circuit will be packaged using a chip-on-board package type designed by SERMA Microelectronics. Furthermore, a second peripheral padring gives individual access to most of the High Voltage features of the XFAB XH018 technology (MOS, DIODES, ESD protection).

The CDR is one of the most important milestones in the project and all the partners are looking forward to the next steps : wafer foundry, prototype blind assembly, industrialization, samples manufacturing and screening, samples electrical and radiation validation and qualification at silicon level.