PROMISE ecosystem and IPs presented to the CNES/COMET-MCE on 15th of November 2024

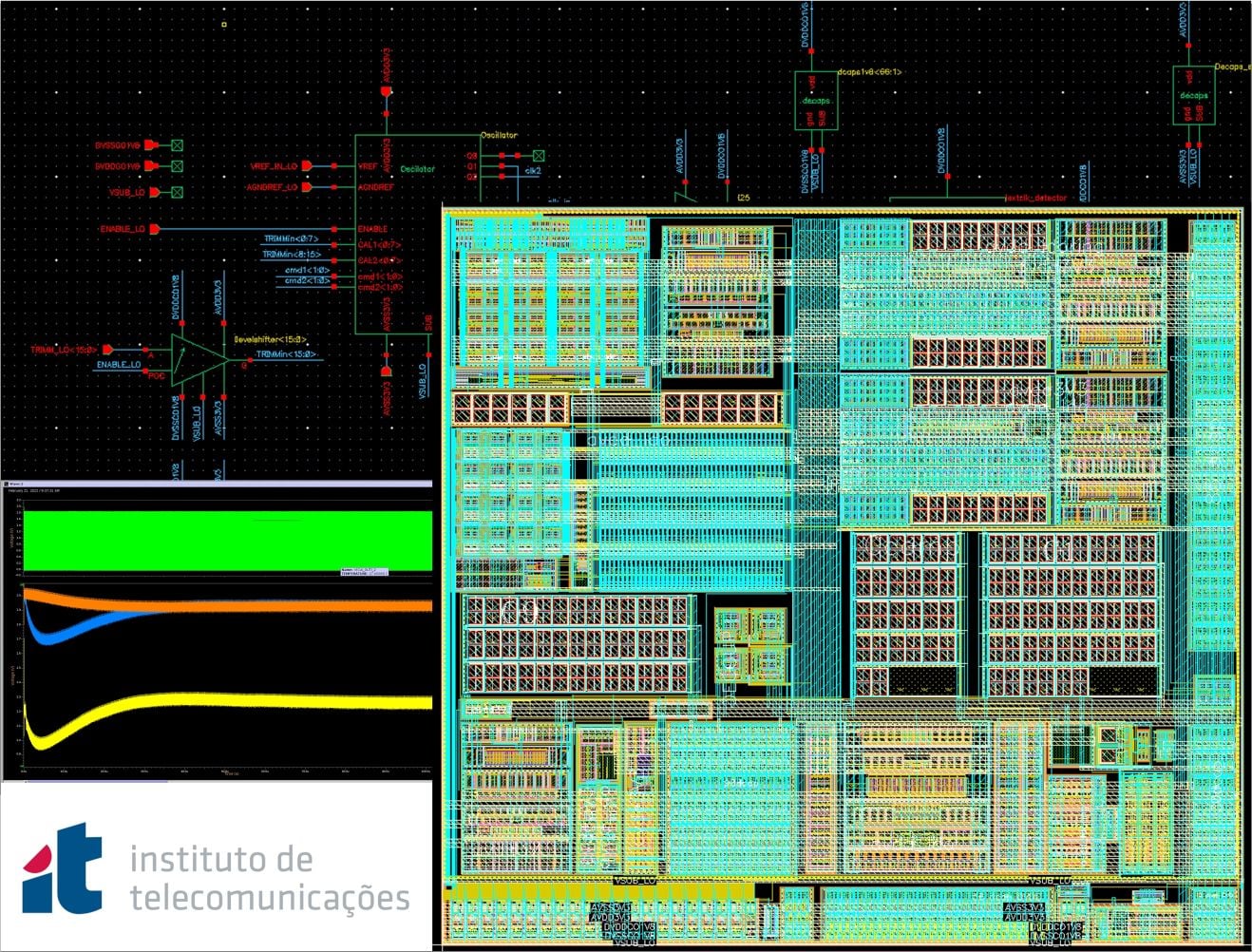

Thales Alenia Space in France, as a partner in the PROMISE consortium and a user of PROMISE IPs in the ongoing SCOPS design, participated in the COMET-MCE “Panorama des Librairies d'IP pour le design en microélectronique”. The presentation covered : PROMISE consortium, PROMISE offer, Pilot Circuit demonstrator and IPs ID...