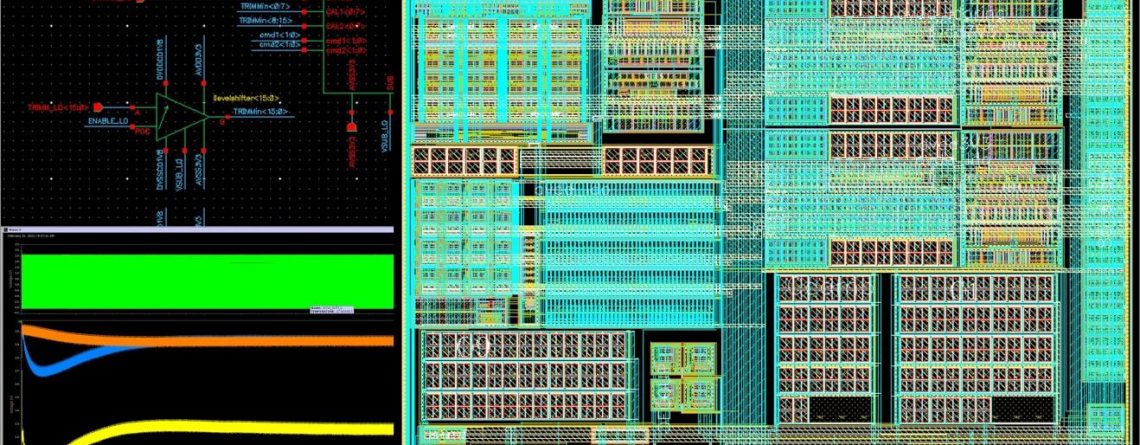

PROMISE LO IP CDR Milestone successfully reached

IT announces the completion of the LO IP. The LO presents a 16MHz on-chip oscillator based on a frequency-locked loop (FLL) which is radiation hardened by design and intended for space applications. The oscillator maintains a temperature stability lower than 50ppm/ºC over process, voltage and temperature variations and low jitter,...

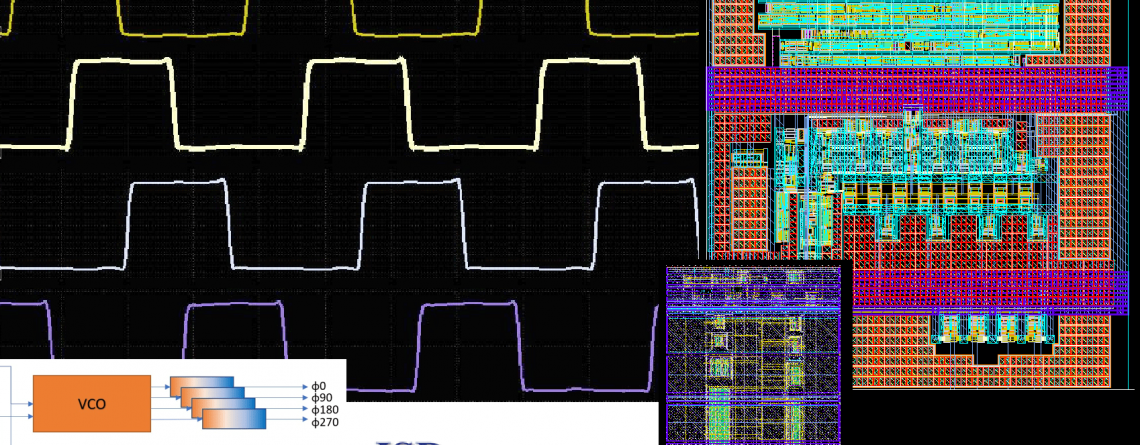

PROMISE PLL IP CDR Milestone successfully reached

ISD announces the completion of the PLL IP. An associative block that enables the PLL to operate with a reference clock from multiple sources (Crystal Oscillator, digital clock or sine wave) and a CMOS Output buffer that will enrich the existing DARE180XH_IO library are included in the CDR data package. The...

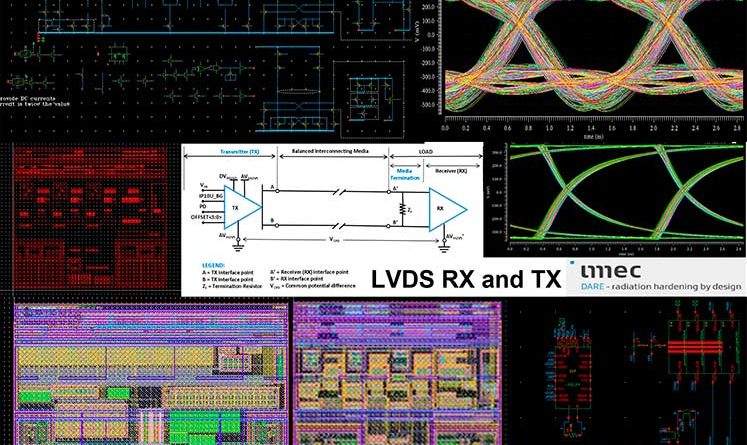

PROMISE LVDS IP CDR Milestone successfully reached

IMEC can announce the successful completion of its DARE radiation hardened LVDS IO simulated up to 720MHz as part of its contribution to the PROMISE project.

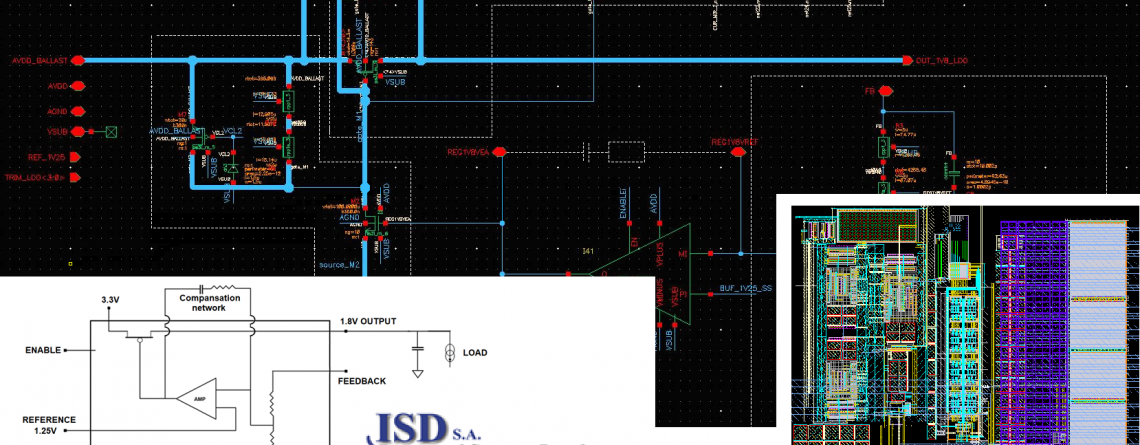

PROMISE 1.8V LDO regulator IP CDR Milestone successfully reached

ISD announces the 500mA - 1.8V LDO design completion; it is a key block that will deliver supply to any digital core using PROMISE library. After delivery of the data-package it passed successfully the CDR milestone.

PROMISE core standard cells, level shifters, IOs and IO/POC IP CDR Milestone successfully reached

After a first successful phase of collaboration with IMEC, that led to a set of optimized radiation hardened standard cells for best PPAs (Power, Performances, Area) covered in task 2.1 of WP2, Menta has successfully delivered on schedule to the PROMISE project, its radiation hardened embedded FPGA (eFPGA) IP that...