Work plan, Work packages and deliverables

Overall structure of the Work plan

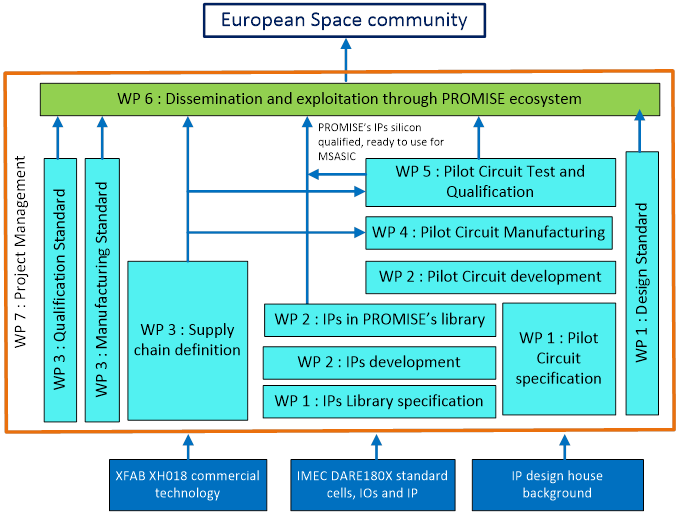

The overall approach for the activities is summarized in the next figure:

The first steps in WP1 are devoted to set the frame of the IP portfolio that will be made available for the Space Community. This is the first Pillar of the PROMISE vision. The end-user will specify the IPs and the Pilot Circuit. The Design Standard will be defined to support the design activities; the Design Standard will include all the design flow and recommendations to guarantee the accessibility and easy reuse of those IPs: interface standards, rules and methods for accessing to the IPs, IP documentation standards.

Based on the XFAB XH018 technology, the existing IMEC DARE180X libraries, design houses background and the Design Standard, hardened IPs will be designed by partner design houses in WP2. When designed, the IPs is gathered in the PROMISE library after a sanity check. The Pilot Circuit is then developed using the IPs in compliance with the Pilot Circuit specification. The Pilot Circuit design will demonstrate the capability of the IPs to be used in a Mixed-Signal ASIC design flow. Main output of the WP2 is the GDSII file to be transferred to the XFAB European foundry for mask process.

In parallel of the Pilot Circuit development, the Supply chain definition activities are run in WP3: this is the second Pillar of the PROMISE vision. The first step is to define the Manufacturing Standard and the Qualification Standard; then all the actors compliant with those Standards will be identified in Europe. When all different actors of a complete supply chain will be identified, a full supply chain will be selected and aligned to manufacture and qualify the PROMISE Pilot Circuit as a proof of its proper integration and operation.

In WP4 and while the Pilot Circuit is under wafer foundry at XFAB, the industrialization Supply Chain activities will develop all the hardware and software to support Pilot Circuit manufacturing and qualification : package design and manufacturing, screening tests on automated tester and burn in & HTOL bench. As soon as wafers are available, the Supply Chain will use those means to assemble the Pilot Circuit (100 and 200 samples) in its package, to submit the samples to screening and globally demonstrate the Supply Chain performance, from design to manufacturing.

The WP5 Test and Qualification is the final step in the validation of the PROMISE developments. Here, the laboratory electrical validation test means and the radiation test means will be developed to be ready when the Pilot Circuit samples are available, the Pilot Circuit will be electrically validated, radiation evaluated (TID and SEE) and silicon qualified on a project based qualification. No assembly qualification is foreseen because package type and assembly process used to manufacture the Pilot Circuit will be already widely used in space applications. The results of all the tests and of the qualification will be analysed and a clear compliance status will be reported. After this WP5, the entire PROMISE library and supply chain will be evaluated and ready to be adopted by the Space Community for the development of mixed signal ASICs.

The WP6 Dissemination and exploitation focuses on the third pillar of the PROMISE vision, the fast adoption of the libraries, supply chain and methodologies by the Space Community. To do so, this WP covers all public communication actions, implementation of all dissemination and exploitation actions of the project results, as well as management of the commercialization and IPR aspects. It shall also include a specific task for community building to foster the creation of a network of PROMISE actual and potential users as a way to push the PROMISE results into the market.

WP7 Project Management is dedicated to all the aspects of project management: overall coordination and reporting, information flow management, communication between partners of the consortium and advisory board, risk and innovation management.

Second run consideration: due to the wide number of different IPs with also a wide range of technical challenge in terms of performances, a first pass full success is an opportunity with low probability. It is very usual in Mixed-Signal ASIC development plan to include a design improvement phase and to manufacture a second run of the circuit to reach the full compliance. Accordingly part of the WP2 activities are dedicated to the IPs and Pilot Circuit design improvement for a second run, part of the WP4 and WP5 activities are also dedicated to manufacture and test the second Pilot Circuit run.

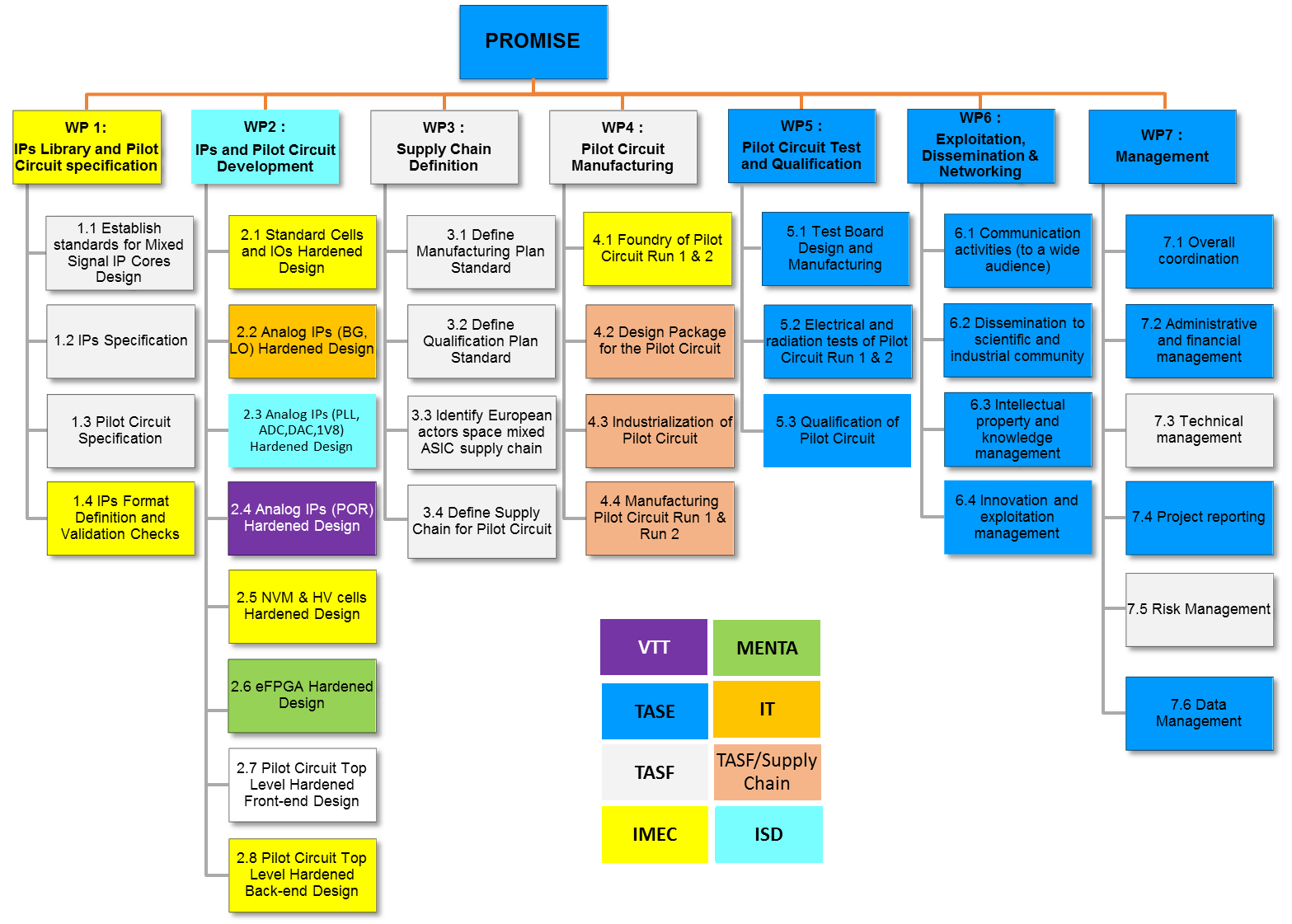

The detail of activities in PROMISE WP is given on the next PERTT chart:

Click image to view full size