# A Scalable Controller for Power Sources (SCOPS)

Date: June 16, 2025

Speaker: Marc Cousineau

The work is part of the European project SCOPS involving satellite manufacturer teams as well as scientific partners. Grant agreement No 101082266.

# **SCOPS**

#### SCALABLE CONTROLLER FOR POWER SOURCES

Coordinator & project manager Architecture / ASIC Design Radiation & End-user tests

Architecture, Know-how & Patents

embracing a better life DARE180XH library, X-FAB foundry

Design & Test validation

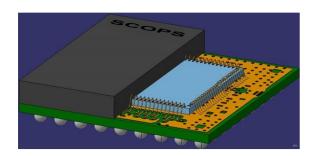

Fully Scalable

Microprocessor Power

Supply

Prototype manufacturing

# **SCOPS** requirements

#### Main performances goal

- To supply future UDSM ASIC & FPGA (Low voltage High current)

- Power DCDC converter control for low output voltage (≥ 0.6V), high current (≤ 200A)

- Current sharing (parallel operation) up to 10 converters

- 250 kHz to 3 MHz

- Radiation hardened : no SEL, no SEFI, no SET, no SEU and TID 100krad

- Chip size 6mm x 5mm

- SMD package of BGA 81, 1mm pitch

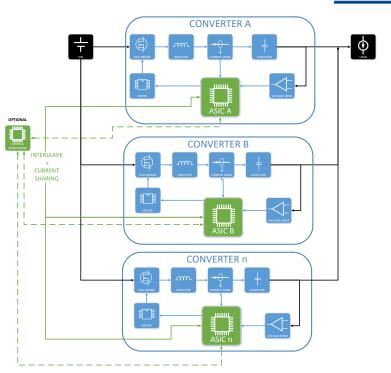

## 1. INTRODUCTION – DECENTRALIZED CONTROL CONCEPT

### Fault tolerant & full operational Power Supply

Fully scalable

No supervisor required

Auto-reconfiguration (Fault-tolerant)

#### #1 – Interleaved Carrier Generation (CG) Block

#### Principle of auto-interleaved Carrier Generation

$$\phi_{\Delta t} = \underbrace{\phi_{i+1}}_{\text{next}} - \phi_i = \phi_i - \underbrace{\phi_{i-1}}_{\text{prev.}} = \frac{2\pi}{N}$$

☐ We need to place each carrier rigorously at the center of next and previous carriers. So we need sure that:

#### A chain of Inter-ASIC communications.

Each ASIC exchanges information with its close neighbors

#### How does it works?

Generation of a relative position error signal

#### #1 – Interleaved Carrier Generation (CG) Block

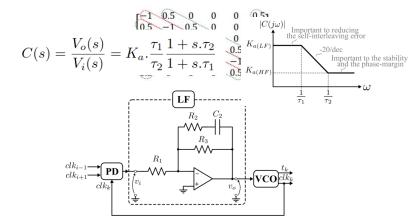

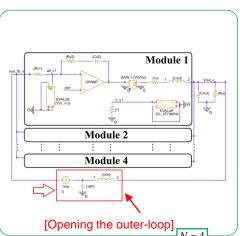

#### Implementation: a 2-inputs PLL circuit

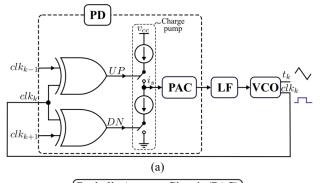

2I-PLL overview for local k-th module example.

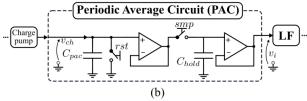

(a) PD block. (b) PAC block

#### Low-pass filter and stability concerns

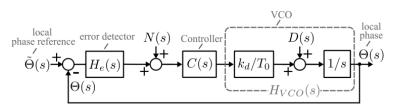

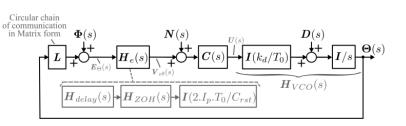

Control block diagram of a single-loop representing one LC elements.

$$\tilde{\Theta}(s) = \frac{1}{2} \underbrace{\Theta_{k+1}(s)}_{\text{next}} + \frac{1}{2} \underbrace{\Theta_{k-1}(s)}_{\text{previous}}$$

$$H_e(s) = \underbrace{e^{-s.(T_0/2)}}_{H_{delay}(s)} \cdot \underbrace{\frac{1 - e^{-s.(T_0).}}{s.(T_0)}}_{H_{ZOH}(s)} \cdot \underbrace{\frac{2.I_p.T_0}{C_{rst}}}_{\text{charge pump}}$$

$$H_{VCO}(s) = \frac{1}{s} \cdot \frac{k_d}{T_0}$$

Generation of an relative position error signal

#### AMIC

#### #1 – Interleaved Carrier Generation (CG) Block

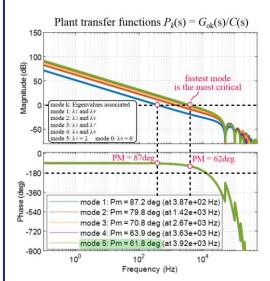

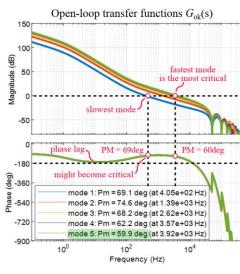

#### Corrector design and modal response

#### Modal response

Modal response with a simple proportional for C(s)

Modal response with C(s)

#### #1 – Interleaved Carrier Generation (CG) Block

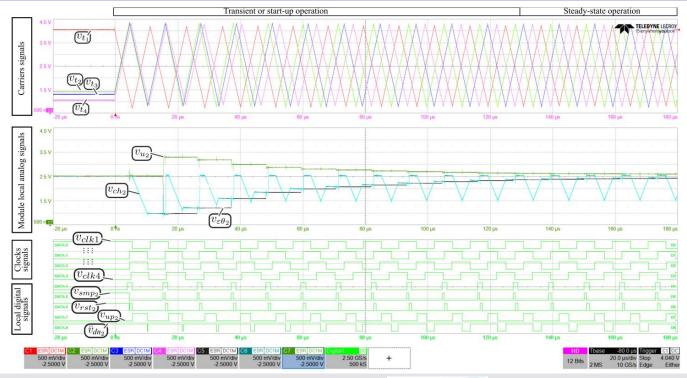

#### Experimental results

Experimental results. (a) Set-up overview. (b) Proof-of-concept board with 6 local controller boards and shared functions.

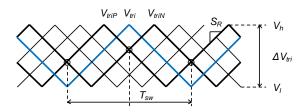

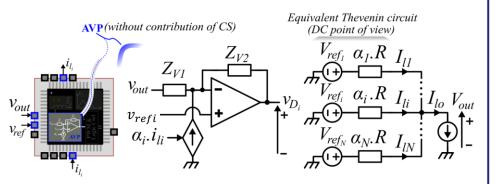

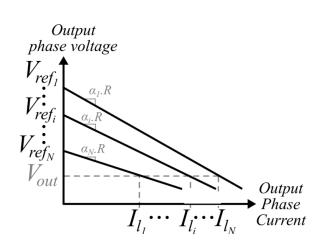

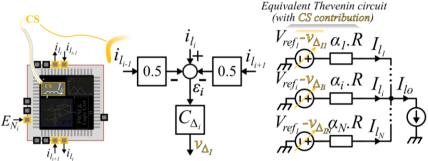

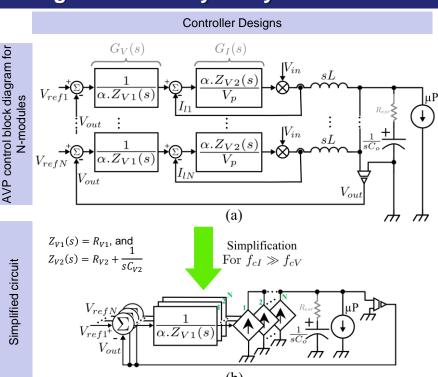

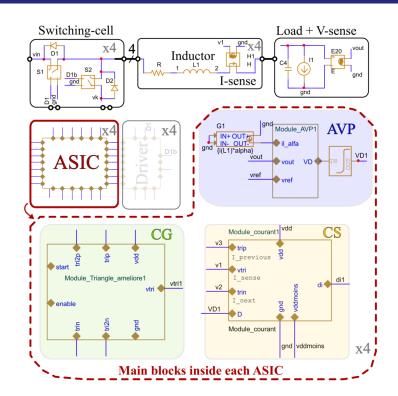

#### #2 – Adaptive Voltage Positioning (AVP) Block

#### Decentralized AVP Principle

- ☐ Each module determines its own duty-cycle

- A drop control method is used

$$V_{out} = V_{ref_i} - \alpha_i.R.I_{l_i},$$

Local voltage reference

Drop control

Output characteristic (load-line or droop or drop)

- ☐ Mismatches between modules must be considered

- ☐ Resulting in unbalanced currents

# AMICS

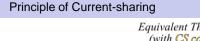

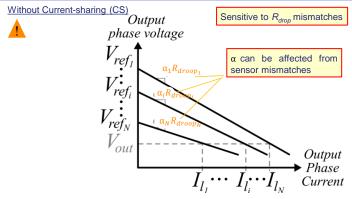

#### #3 – Current-sharing (CS) Block

$$e_i(t) = i_{l_i}(t) - 0.5\underbrace{(i_{l_{i+1}}(t) - i_{l_{i-1}})}_{\text{next}}; \qquad C_{\Delta_i}(s) = \underbrace{V_{\Delta_{Ii}}(s)}_{E_i(s)} = \underbrace{-K_{\Delta i}}_{\text{Closed-loop time Tuned to response guarantee system}} \underbrace{1 + \tau_{\Delta i}.s}_{\text{guarantee system}}$$

- The CS function is decentralized.

- □ CS functions balance the phase currents by adjusting the relative position of the characteristics.

- ☐ Thanks to the ring communication, it becomes easy to remove a module from the chain.

#### Phase current balacing

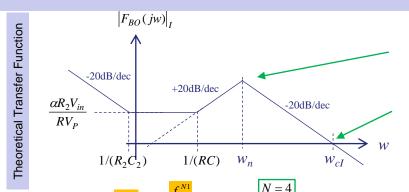

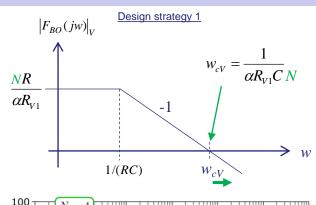

#### **#Design and Stability Analysis**

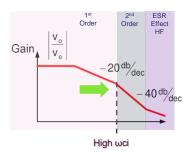

☐ A high wci can simplify the buck converter from a 2<sup>nd</sup>-order system to a 1st-order system (i.e., the inductor becomes a voltage-controlled current source).

$$R_{V1} = \frac{1}{\alpha}.\frac{\Delta V}{I_{L_{Max}}};$$

$$f_{cV} = \frac{1}{2\pi} \cdot \frac{1}{\alpha R_{V1}} \cdot \frac{N}{C_o},$$

$$f_{cI} = \frac{1}{2\pi} \cdot \frac{V_{in}}{V_p} \cdot \frac{\alpha R_{V2}}{L},$$

Expected open-loop transfer function

☐ Frequency relationship and Guidelines. Make sure to

$$\omega_{sw}>>\omega_{cTi}>>\omega_{cT2}$$

$\omega_{cTi}=0.33\omega_{sw}$  and  $\omega_{cTv}=0.1\omega_{sw}$

$$f_{cI} = \frac{1}{3} f_{sw}; \quad f_{cV} = \frac{1}{10} f_{sw};$$

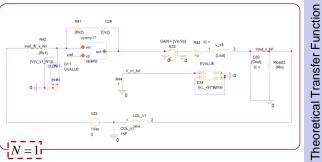

Simplified circuit

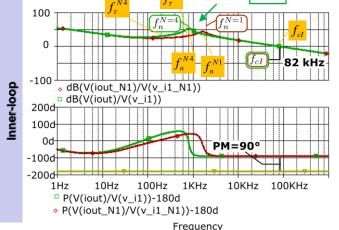

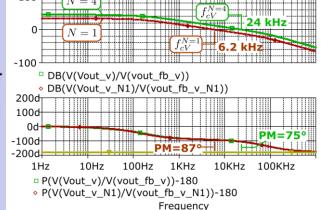

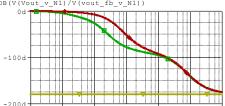

# # Simulation results (Frequency-domain)

☐ Impact of *N* in the current loop (Inner loop)

#### Note:

- ☐ There is no change in current loop bandwidth

- $\square$   $f_n^N$  variation is lower than  $f_\tau$  with N variation

- $\square$   $f_n^N$  and  $f_\tau$  change as long as N and  $C_{out}$  changes

- ☐ Open-loop Unconditionally stable

#### # Simulation results (Frequency-domain)

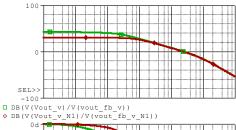

#### ☐ Impact of *N* in the voltage loop (Outer-loop)

#### Design strategy 2

If  $C_o$  value is normalized as  $C'_o = C_o/N$  in one-module there is no change in HF

$$f_{cV} = \frac{1}{2\pi} \cdot \frac{1}{\alpha R_{V1}} \cdot \frac{N}{N.C_o'} = \frac{1}{2\pi} \cdot \frac{1}{\alpha R_{V1}} \cdot \frac{1}{C_o'}$$

□ P(V(Vout\_v)/V(vout\_fb\_v))-180

◆ P(V(Vout\_v\_N1)/V(vout\_fb\_v\_N1))-180 ▼ -180d

Frequency

1.0Hz 10Hz

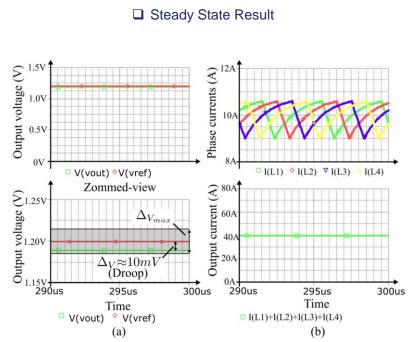

#### # Simulation results (Time-domain)

Main specifications for simulation tests of the system.

| Parameters         | Value                                                      | Description                          |

|--------------------|------------------------------------------------------------|--------------------------------------|

| $f_{sw}$           | 250  kHz                                                   | Switching frequency                  |

| N                  | 4                                                          | Number of Phases                     |

| $I_{out}$          | 40 - 100 A                                                 | Output current range                 |

| $I_{ph}$           | 10 - $25 A$                                                | Phase current range                  |

| $V_{out}$          | 0.6 - $1.2~V$                                              | Output voltage range                 |

| $V_{in}$           | 3 - $12~V$                                                 | Input voltage range                  |

| $\Delta_{V_{max}}$ | $30~\mathrm{m}V$                                           | Maximum admissible                   |

|                    |                                                            | output voltage range                 |

| $\alpha$           | 0.01 m                                                     | Effective current sensor sensitivity |

| $R_{V1}$           | 100 Ω                                                      | AVP-Controller $Z_{V1}(s)$           |

| $R_{V2}$           | $19.6~\mathrm{k}\Omega$                                    | AVP-Controller $Z_{V2}(s)$           |

| $C_{V2}$           | 50 nF                                                      | AVP-Controller $Z_{V2}(s)$           |

| $\alpha R_{V1}$    | $\left(\begin{array}{c} 1 \text{ mV/A} \end{array}\right)$ | AVP Slope per phase                  |

|                    | _                                                          |                                      |

# AMICSA

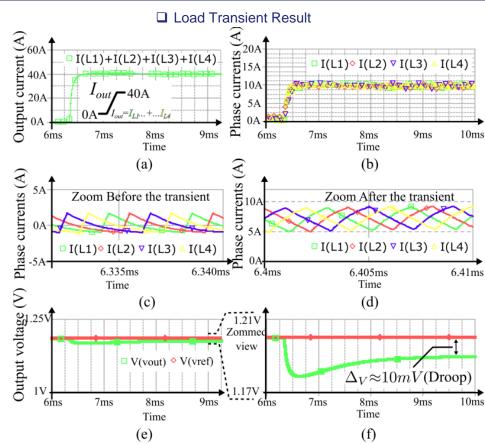

#### # Simulation results (Time-domain)

Fig. 10. Simulation result. Steady-state waveforms. (a) Output voltage. (b) Phase currents (on the top) and Output current (on the bottom).

#### **# Simulation results (Time-domain)**

#### □ CG Block simulation with reconfiguration test

Experimental setup. (a) Start-up

(b) Reconfiguration from 4 to 3 phases

(c) Reconfiguration from 3 to 4 phases

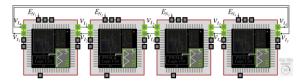

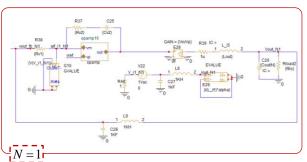

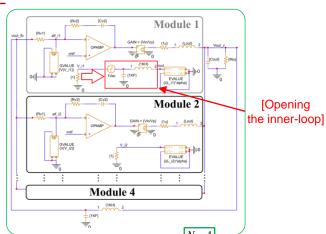

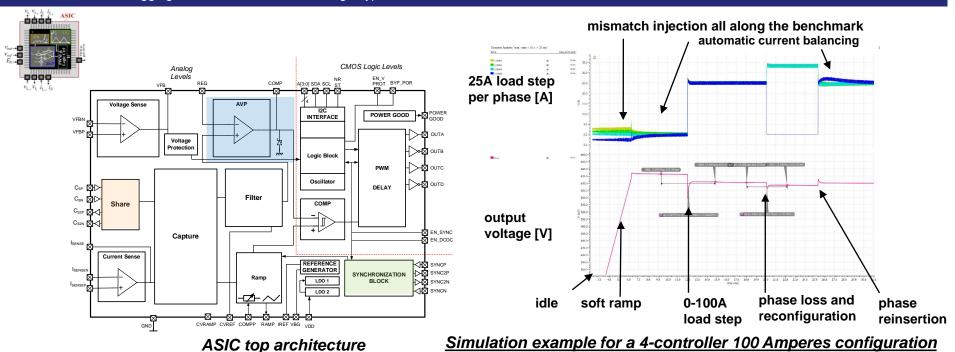

#### 3. ANALOG BEHAVIORAL MODELING AND IMPLEMENTATION

- ✓ Prior to the ASIC design phase, a detailed model was developed at sub-block level which allowed :

- the validation of the system architecture down to individual functions

- the debugging and correction of some design hypothesis

#### 4. ASIC HARDENING FOR SPACE

- the <u>digital control</u> functions are developed using a design methodology to guarantee the good function over the mission profile with:

- ✓ radiation hardened standard cells library

- ✓ auto corrective registers, especially the control of the analog part.

- ✓ lock free state machines (prevent loss of functionality due to register upset or SEFI)

- system resilient to unexpected reset with a transparent reinsertion of a circuit.

- At system level, mismatch and events were injected during the simulations to harden the <u>analog part</u> to the right need (no excess design nor underdesign), especially for:

- current sensing and sharing with other circuits.

- ✓ voltage sensing and adaptive voltage positioning.

- ✓ pulse with modulation with non overlapping outputs by design

- √ inter-circuit synchronization or standalone operation.

- √ integration of electrical constraints of large PCBs.

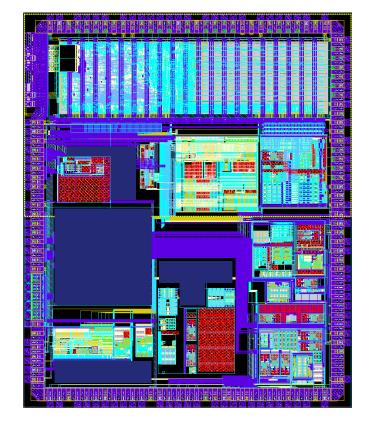

- At top level, mixed signal simulations (digital RTL code + analog at transistor level) to guarantee the right control, connections, and generate test patterns for industrialization.

ASIC Layout (X-Fab 180nm XH018, 5x6 mm²)

### 4. CONCLUSIONS AND FUTURES WORKS

#### Conclusions

- A <u>decentralized control concept</u> applied to a multiphase interleaved synchronous buck converter suitable <u>for power management in satellites</u> <u>systems</u> has been presented.

- Three main features of each local ASIC: i) the <u>self-interleaved</u> carriers/PWM signals, ii) Local <u>AVP voltage regulation</u>, iii) and local the current-sharing capability.

- Possibility to improve system functional safety thanks to:

- Modularity and Scalability

- ☐ Fault-tolerance and auto-reconfiguration capability (operation with N-1 active phases is guaranteed under a faulty condition).

- □ Local controllers connected in a circular chain of communications.

- ☐ The proposed method and theoretical expectations are validated by SPICE simulations and lab. prototypes,

# **ACKNOWLEDGMENT**

- ☐ This project has received funding from the European Union's Horizon Europe research and innovation program under grant agreement No 101082266.

- ☐ The authors acknowledge the active contribution of

- ☐ Thales Alenia Space,

- □ LAPLACE laboratory, Institut National Polytechnique de Toulouse

- ☐ ISD,

- Synergie CAD,

Toulouse),

□ and IMEC.

# **THANK YOU**

Visit our website for more: https://scopsproject.eu/