| DELIVERABLE: | D1.3 - Interface Standards<br>& IP Usage Definition |

|--------------|-----------------------------------------------------|

| DATE:        | 23/04/2020                                          |

|              |                                                     |

**ISSUE:** 002 Page: 1/27

# **PROMISE**

# WP1 IPs Library and Pilot Circuit **Specification**

# **D1.3 Interface Standards & IP Usage Definition**

| Written by                    | <b>Responsibility</b><br>+ handwritten signature if no electronic workflow tool |

|-------------------------------|---------------------------------------------------------------------------------|

| IMEC / Giancarlo Franciscatto | R&D Engineer                                                                    |

| IMEC / Geert Thys             | WP1 contributor                                                                 |

| Verified by                   |                                                                                 |

| TAS-F / Philippe Ayzac        | Technical Coordinator                                                           |

| ISD / Dimitri Baramilis       | WP contributor                                                                  |

| VTT / Kari Tukkiniemi         | WP contributor                                                                  |

| Approved by                   |                                                                                 |

| IMEC / Laurent Berti          | WP1 Leader                                                                      |

| TAS-S / Filip Veljković       | Project Coordinator                                                             |

mec

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| Deliverable:<br>Date: |     | erface Standards<br>je Definition<br>0 |

|-----------------------|-----|----------------------------------------|

| ISSUE:                | 002 | Page: 2/27                             |

# CHANGE RECORDS

| DATE       | § CHANGE RECORDS                           | AUTHOR                       |

|------------|--------------------------------------------|------------------------------|

| 16/03/2020 | Document creation                          | G. Franciscatto              |

| 23/04/2020 | Final version after reviews for submission | G. Franciscatto              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            |                                            |                              |

|            | 16/03/2020                                 | 16/03/2020 Document creation |

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

**DELIVERABLE:** D1.3 - Interface Standards & IP Usage Definition 23/04/2020 DATE:

002 **ISSUE:**

### Page: 3/27

# TABLE OF CONTENTS

| 1. | INTR  | ODUCTION                                                                                                                     | 5  |

|----|-------|------------------------------------------------------------------------------------------------------------------------------|----|

|    | 1.1.  | SCOPE AND PURPOSE                                                                                                            | 5  |

|    | 1.2.  | APPLICABLE DOCUMENTS                                                                                                         | 5  |

|    | 1.3.  | Reference documents                                                                                                          | 5  |

|    | 1.4.  | DEFINITIONS AND ACRONYMS                                                                                                     | 6  |

|    | 1.5.  | DOCUMENT OUTLINE                                                                                                             | 7  |

| 2. | IP DE | LIVERABLES [IPDE]                                                                                                            |    |

|    | 2.1.  | IP VIEW CLASSIFICATION                                                                                                       |    |

|    | 2.2.  | IP VIEWS                                                                                                                     | 9  |

|    | 2.3.  | PACKAGE STRUCTURE                                                                                                            | 11 |

|    | 2.4.  | VERSION TAGGING                                                                                                              | 14 |

| 3. | DELIV | VERABLE DATA VALIDATION [DDVA]                                                                                               | 15 |

|    | 3.1.  | SINGLE VIEW CHECKS                                                                                                           | 15 |

|    | 3.2.  | CROSS-VIEW CHECKS                                                                                                            | 16 |

| 4. | DESIG | GN FLOWS [DFLW]                                                                                                              | 17 |

|    | 4.1.  | ANALOG-ON-TOP FLOW                                                                                                           | 17 |

|    |       | <ul><li>.1. Analog Design Flow Using Full Design Views</li><li>.2. Analog Design Flow Using Black-Box Design Views</li></ul> |    |

|    | 4.2.  | DIGITAL-ON-TOP FLOW                                                                                                          |    |

|    | 4.3.  | Mixed-Signal Design                                                                                                          | 22 |

| 5. | COMI  | PLIANCE MATRIX                                                                                                               | 22 |

ເກາec

1

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| DELIVERABLE: |           | erface Standards<br>je Definition |

|--------------|-----------|-----------------------------------|

| DATE:        | 23/04/202 |                                   |

| ISSUE:       | 002       | Page: 4/27                        |

# LISTE DES OBJETS

| Requirement IS-DDVA-16 | 15 |

|------------------------|----|

| Requirement IS-DDVA-17 | 15 |

| Requirement IS-DDVA-18 | 15 |

| Requirement IS-DDVA-19 | 16 |

| Requirement IS-DFLW-20 | 17 |

| Requirement IS-DFLW-21 | 17 |

| Requirement IS-DFLW-22 | 20 |

| Requirement IS-DFLW-23 | 22 |

| Requirement IS-IPDE-01 | 8  |

| Requirement IS-IPDE-02 | 8  |

| Requirement IS-IPDE-03 | 8  |

| Requirement IS-IPDE-04 | 8  |

|                        |    |

| Requirement IS-IPDE-05 | 8  |

|------------------------|----|

| Requirement IS-IPDE-06 | 9  |

| Requirement IS-IPDE-07 | 9  |

| Requirement IS-IPDE-08 | 9  |

| Requirement IS-IPDE-09 | 11 |

| Requirement IS-IPDE-10 | 11 |

| Requirement IS-IPDE-11 | 14 |

| Requirement IS-IPDE-12 | 14 |

| Requirement IS-IPDE-13 | 14 |

| Requirement IS-IPDE-14 | 14 |

| Requirement IS-IPDE-15 | 14 |

|                        |    |

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

## **1. INTRODUCTION**

### **1.1. SCOPE AND PURPOSE**

This document contains the specification of the different interfaces and documents to be used in the IP delivery in order to guarantee the cross-compatibility of the IPs as well as compatibility with the common PROMISE design flow. The usage of the IP views within the design flow will be indicated.

### **1.2.** APPLICABLE DOCUMENTS

None

### **1.3. REFERENCE DOCUMENTS**

| Internal<br>code /<br>DRL | Reference | Title                                                         | Location of record                                  |

|---------------------------|-----------|---------------------------------------------------------------|-----------------------------------------------------|

| RD1                       | IPP 1 3.0 | Virtual Component Identification<br>Physical Tagging Standard | http://vsia.org/docs/IPP_Tagging<br>_Std%201_30.pdf |

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

#### 1.4. **DEFINITIONS AND ACRONYMS**

| ADC   | Analog-to-Digital Converter                   |

|-------|-----------------------------------------------|

| ASIC  | Application Specific Integrated Circuit       |

| CDL   | Circuit Description Language                  |

| CDF   | Component Description Format                  |

| DARE  | Design Against Radiation Effects              |

| DB    | Database                                      |

| DEF   | Design Exchange Format                        |

| DRC   | Design Rule Check                             |

| GDSII | Graphic Design System II                      |

| HDL   | Hardware Description Language                 |

| HTML  | HyperText Markup Language                     |

| I/O   | Input/Output                                  |

| IBIS  | Input/Output Buffer Information Specification |

| IP    | Intellectual Property                         |

| LEF   | Library Exchange Format                       |

| LPE   | Layout Parameter Extraction                   |

| LVS   | Layout Versus Schematic                       |

| NDA   | Non-Disclosure Agreement                      |

| OA    | OpenAccess                                    |

| PDF   | Portable Document Format                      |

| PEX   | Parasitic Extraction                          |

| PVS   | Physical Verification System                  |

| RAD   | Radiation Design                              |

| RTL   | Register-Transfer Level                       |

| SDC   | Synopsys Design Contraint                     |

| SDF   | Standard Delay File                           |

| SPEF  | Standard Parasitic Exchange Format            |

| SVRF  | Standard Verification Rules Format            |

| VHDL  | Very High-level Design Language               |

| VITAL | VHDL Initiative Towards ASIC Libraries        |

| VSIA  | Virtual Socket Interface Alliance             |

ເກາຍດ

1

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| Deliverable:<br>Date: |     | erface Standards<br>e Definition<br>0 |

|-----------------------|-----|---------------------------------------|

| ISSUE:                | 002 | Page: 7/27                            |

#### 1.5. **DOCUMENT OUTLINE**

Section 1 describes the purpose, scope and application field of this document. In addition, it gives useful information for a better understanding of the document such as applicable documents, reference documents, specific definitions used or refer to in the document and at least the list of acronyms used. A brief presentation of its content completes this section

Section 2 describes IP deliverable views and package standard structure to be adopted by all IP providers in the context of PROMISE project.

Section 3 describes minimum validation steps to be performed on IP deliverables upon release.

Section 4 describes the use of deliverable IP views in analog-on-top and digital-on-top design flows as well as their application in the design of mixed-signal applications.

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

### This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium Produced by SUMO V7.7

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358 PUBLIC DOCUMENT

nec embracing a better life

**DELIVERABLE:** D1.3 - Interface Standards & IP Usage Definition 23/04/2020 DATE:

ISSUE: 002 Page: 8/27

#### 2. **IP DELIVERABLES [IPDE]**

Requirement IS-IPDE-01 :

IP deliverables refer to the set of library or IP views provided by any partner design house.

Requirement IS-IPDE-02 :

IP deliverable data will be distributed in tarball compressed package files containing views and documentation arranged in a predefined directory structure.

Requirement IS-IPDE-03 :

Each deliverable package file will combine data for a single IP.

[vmethod: Analysys]

Requirement IS-IPDE-04 :

Each IP will have its own serial version tag number indicated in package file name and package directory structure.

[vmethod: Analysys]

#### 2.1. **IP VIEW CLASSIFICATION**

orizon 2020 uropean Union Funding or Research & Innovatio

Requirement IS-IPDE-05 :

IP views are classified in different distribution categories:

- Public: views distributed without restriction to anyone.

- Restricted: views suitable for distribution to any user under NDA.

- Private: sensitive proprietary data only disclosed to selected partners under special NDA.

Packages variants will be created for every IP to combine views for each distribution scope.

[vmethod: Analysys]

[vmethod: Analysis]

|      | Deliverable:<br>Date: |         | D1.3 - Interface Standards<br>& IP Usage Definition<br>23/04/2020 |  |

|------|-----------------------|---------|-------------------------------------------------------------------|--|

| MISE | DATE.                 | 23/04/2 | .020                                                              |  |

|      | ISSUE:                | 002     | Page: 9/27                                                        |  |

### 2.2. IP VIEWS

Requirement IS-IPDE-06 :

The table below indicates a minimum set of recommended IP views that should be distributed in order to support digital and analog design flows. Certain views apply only to selected types of IP blocks, as indicated in the table.

[vmethod: Analysys]

Requirement IS-IPDE-07 :

This list is not exhaustive as additional views may be required for certain IPs.

[vmethod: Analysys]

Requirement IS-IPDE-08 :

IP providers and users should agree on the list of deliverable views for each IP before its release, for instance during requirement specification or IP design review.

[vmethod: Analysys]

| View Name                                                                                                                      | Requirements               | Required for<br>digital flow | Required for<br>analog flow | Distribution |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|-----------------------------|--------------|

| Product brief                                                                                                                  | PDF                        | Yes                          | Yes                         | Public       |

| Release notes                                                                                                                  | PDF                        | Yes                          | Yes                         | Public       |

| User manual with integration guidelines                                                                                        | PDF                        | Yes                          | Yes                         | Restricted   |

| Black-box OA library <ul> <li>Symbol</li> <li>Spectre</li> <li>Eldo</li> <li>auCdl</li> <li>auLvs</li> <li>Abstract</li> </ul> | Cadence IC61<br>compatible | No                           | Yes                         | Restricted   |

| Black-box CDL netlist                                                                                                          |                            | No                           | Yes                         | Restricted   |

| LEF                                                                                                                            | DEF/LEF<br>version 5.8     | Yes                          | No                          | Restricted   |

| Encrypted LPE Spectre netlist                                                                                                  | Cadence IC61 compatible    | No                           | Yes                         | Restricted   |

| Encrypted LPE Eldo netlist                                                                                                     |                            | No                           | Yes                         | Restricted   |

| Liberty file                                                                                                                   |                            | Yes                          | No                          | Restricted   |

| Synopsys compiled DB library                                                                                                   |                            | Optional                     | No                          | Restricted   |

| Datasheets with Liberty<br>information                                                                                         | PDF or HTML                | Optional                     | Optional                    | Restricted   |

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

**DELIVERABLE:** D1.3 - Interface Standards & IP Usage Definition 23/04/2020 DATE:

002

**ISSUE:**

Page: 10/27

| View Name                                                                | Requirements                   | Required for<br>digital flow | Required for<br>analog flow | Distribution |

|--------------------------------------------------------------------------|--------------------------------|------------------------------|-----------------------------|--------------|

| Verilog library models with timing annotation                            | SDF version 3.0                | Yes                          | No                          | Restricted   |

| VITAL library models with timing information                             | SDF version 3.0                | Optional                     | No                          | Restricted   |

| Verilog-A models (analog IP only)                                        |                                | Yes                          | Yes                         | Restricted   |

| IBIS models (digital I/O only)                                           | IBIS version 4.2<br>or greater | Yes                          | Yes                         | Restricted   |

| SPEF file (eFPGA only)                                                   |                                | Yes                          | No                          | Restricted   |

| GDSII layout                                                             |                                | Yes                          | Yes                         | Private      |

| CDL netlist                                                              |                                | Yes                          | Yes                         | Private      |

| LPE Spectre netlist                                                      |                                | No                           | Yes                         | Private      |

| LPE Eldo netlist                                                         |                                | No                           | Yes                         | Private      |

| OA library <ul> <li>Symbol</li> <li>Schematic</li> <li>Layout</li> </ul> | Cadence IC61<br>compatible     | No                           | Yes                         | Private      |

1

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| DELIVERABLE: | D1.3 - Interface Standards<br>& IP Usage Definition |             |  |

|--------------|-----------------------------------------------------|-------------|--|

| DATE:        | 23/04/202                                           |             |  |

| ISSUE:       | 002                                                 | Page: 11/27 |  |

### **2.3.** PACKAGE STRUCTURE

Requirement IS-IPDE-09 :

All package views will be arranged in a standardized directory structure as shown below. File names and extensions for each view are indicated in this template.

[vmethod: Analysys]

Requirement IS-IPDE-10 :

Additional views not foreseen in this document should be placed in separate subdirectories at the same level as other views, under *Back\_End*, *Front\_End* or *Documentation* directories, depending on which design phase they are mainly used.

[vmethod: Analysys]

| PLATFOR          | _               | רא דע                               | 2                          | e.g. DARE180XH<br>e.g. IO<br>See paragraph 0                                        |

|------------------|-----------------|-------------------------------------|----------------------------|-------------------------------------------------------------------------------------|

|                  | Ba              | _                                   |                            | Directory for back-end design views                                                 |

|                  |                 | - gds                               | A                          | Directory for back-end design views                                                 |

|                  |                 | -                                   | METAL_STACK_NAME           | e.g. 1143                                                                           |

|                  |                 |                                     | ` PLATFORM IP NAME.gds.gz  | e.g. DARE180XH_IO.gds.gz                                                            |

|                  |                 | - lef                               |                            | 0.g. D/1/2 100/11_10.g03.gz                                                         |

|                  |                 |                                     | METAL_STACK_NAME           |                                                                                     |

|                  |                 |                                     | ` PLATFORM_IP_NAME.gds.gz  |                                                                                     |

|                  |                 | - lpe                               |                            | Optional set of PEX corners and parasitic modes                                     |

|                  |                 | -                                   | spectre                    |                                                                                     |

|                  |                 | i                                   | norc                       |                                                                                     |

|                  |                 | ·<br>I                              | PLATFORM IP NAME.min.scs   |                                                                                     |

|                  |                 | i                                   | PLATFORM_IP_NAME.typ.scs   |                                                                                     |

|                  | i i             | i                                   | ` PLATFORM_IP_NAME.max.scs |                                                                                     |

|                  | i i             | i                                   | c                          |                                                                                     |

|                  |                 | i                                   | rc                         |                                                                                     |

|                  |                 | Ì                                   | rcc                        |                                                                                     |

|                  |                 |                                     | eldo                       |                                                                                     |

|                  |                 | Ì                                   | norc                       |                                                                                     |

|                  |                 | I                                   | PLATFORM IP NAME.min.cir   |                                                                                     |

|                  |                 | I                                   | PLATFORM IP NAME.typ.cir   |                                                                                     |

|                  |                 | I                                   | ` PLATFORM IP NAME.max.cir |                                                                                     |

|                  |                 | I                                   | c                          |                                                                                     |

|                  |                 | I                                   | rc                         |                                                                                     |

|                  |                 | I                                   | ` rcc                      |                                                                                     |

|                  |                 | - lpe                               | encrypt                    |                                                                                     |

|                  |                 |                                     | spectre                    |                                                                                     |

|                  |                 | I                                   | norc                       |                                                                                     |

|                  |                 | I                                   | PLATFORM_IP_NAME.min.scs   |                                                                                     |

|                  |                 | I                                   | PLATFORM_IP_NAME.typ.scs   |                                                                                     |

|                  |                 |                                     | ` PLATFORM_IP_NAME.max.scs |                                                                                     |

|                  |                 |                                     | c                          |                                                                                     |

|                  |                 |                                     | rc                         |                                                                                     |

|                  |                 | 20<br>nion Funding<br>h & Innovatio |                            |                                                                                     |

| oject has ro     | eceived fur     | nding fr                            |                            | and innovation programme under grant agreement No                                   |

|                  |                 | -                                   | PUBLIC DOCUMENT            |                                                                                     |

| is document is n | ot to be reprod | uced, mod                           |                            | n part nor disclosed to any third party without the prior written permission of the |

DELIVERABLE:D1.3 - Interface Standards<br/>& IP Usage DefinitionDATE:23/04/2020

**ISSUE:** 002 Page: 12/27 `-- rcc I |-- eldo I |-- norc | |-- PLATFORM IP NAME.min.cir |-- PLATFORM IP NAME.typ.cir `-- PLATFORM IP NAME.max.cir |-- c |-- rc `-- rcc 1 -OA `-- PLATFORM\_IP\_NAME |-- CELL NAME 1 |-- abstract `-- layout.oa |-- auCdl `-- symbol.oa |-- auLvs `-- symbol.oa |-- eldo `-- symbol.oa L |-- layout `-- layout.oa T |-- schematic `-- sch.oa |-- spectre `-- symbol.oa |-- symbol ) `-- symbol.oa `-- data.dm |-- ... `-- CELL\_NAME\_n |-- ibis `-- platform ip name.ibs Lower case file name required by IBIS standard |-- spef |-- cdl `-- PLATFORM\_IP\_NAME.cdl -- cdl bbox |-- PLATFORM IP NAME.svrf SVRF commands for black-box setup `-- PLATFORM IP NAME.cdl - Documentation Directory for documentation files 1 -|-- datasheets |-- CORNER 1 `-- index.html |-- ... `-- CORNER n -- documents |-- PLATFORM IP NAME ProductBrief.pdf `-- PLATFORM\_IP\_NAME\_UG.pdf -- Front End Directory for front-end design views |-- timing power noise |-- PLATFORM IP NAME CORNER 1.lib |-- ... Horizon 2020 European Union Funding for Research & Innovatior ISD SA ເກາຍດ 1 ThalesAlenia menta embracing a better life This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| DELIVERABLE:<br>DATE: |     | erface Standards<br>e Definition<br>0 |

|-----------------------|-----|---------------------------------------|

| ISSUE:                | 002 | Page: 13/27                           |

|   | ` PLATFORM_IP_NAME_CORNER_n.lib  |

|---|----------------------------------|

|   | veriloga                         |

|   | PLATFORM_IP_NAME.va              |

|   | verilog                          |

|   | PLATFORM IP NAME <b>SDF3_0.v</b> |

| ` | vital                            |

|   | PLATFORM_IP_NAME_SDF3_0.vhd      |

|   |                                  |

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| DELIVERABLE:<br>DATE: | D1.3 - Interface Standa<br>& IP Usage Definition<br>23/04/2020 |             |

|-----------------------|----------------------------------------------------------------|-------------|

| ISSUE:                | 002                                                            | Page: 14/27 |

#### **VERSION TAGGING** 2.4.

Requirement IS-IPDE-11 :

IP version tagging intends to enable full traceability of data and versions used in designs.

Requirement IS-IPDE-12 :

IP version numbers should comply to the format  $Vx_y_z$ , where x integer indicates a major update, y integer indicates a minor update, and z indicates a version number relevant internally to the IP provider. Example: DARE180XH\_CORE\_V2.1.349.

[vmethod: Analysys]

[vmethod: Analysys]

Requirement IS-IPDE-13 :

Version numbers must be included in the package name and its directory structure, as shown in paragraph2.3.

[vmethod: Analysys]

Requirement IS-IPDE-14 :

IP version and ownership information should be placed in all documentation, GDSII and textformat views. In the case of text files, header comments can be used, as shown in the example below. IP providers are free to use their own formatting style.

[vmethod: Analysys]

[vmethod: Analysys]

| DARE180XH_PLL.lef:                                    |             |

|-------------------------------------------------------|-------------|

| #**************************************               | * * * * * * |

| #* DARE180XH Platform                                 | *           |

| #* Copyright 2020, imec vzw. All Rights Reserved.     | *           |

| <pre>#* Technical support: dare_support@imec.be</pre> | *           |

| #*                                                    | *           |

| #* Library : DARE180XH_PLL                            | *           |

| #*                                                    | *           |

| #* Release version : 1.0.321                          | *           |

| #* Release date : 22-Apr-2020 23:31                   | *           |

| # * * * * * * * * * * * * * * * * * * *               | * * * * * * |

| VERSION 5.8 ;                                         |             |

| •••                                                   |             |

Requirement IS-IPDE-15 :

In the case of GDSII, tags should be added and encoded in accordance with the VSIA's IP tagging standard (RD1).

| Deliverable:<br>Date: |     | erface Standards<br>e Definition<br>0 |

|-----------------------|-----|---------------------------------------|

| ISSUE:                | 002 | Page: 15/27                           |

# 3. DELIVERABLE DATA VALIDATION [DDVA]

Requirement IS-DDVA-16 :

IP views must be validated upon release to users by its design house. Certain sanity checks will also be performed at imec upon starting top-level designs using deliverables from IP providers.

[vmethod: Analysys]

Requirement IS-DDVA-17 :

A minimum required set of verification procedures is defined in this section.

[vmethod: Analysys]

### **3.1. SINGLE VIEW CHECKS**

Requirement IS-DDVA-18 :

Several verification procedures must be applied on individual IP views.

[vmethod: Analysys]

| Check                                                  | Views                                 | Method<br>(Tool)                | Responsible           |

|--------------------------------------------------------|---------------------------------------|---------------------------------|-----------------------|

| Foundry design rules (DRC)                             | Layout<br>GDSII<br>OA abstract        | Automated<br>(Calibre/PVS)      | IP designer<br>+ imec |

| Foundry antenna rules                                  | Layout<br>GDSII                       | Automated<br>(Calibre/PVS)      | IP designer<br>+ imec |

| DARE layout rules (RAD)                                | Layout<br>GDSII                       | Automated<br>(Calibre)          | IP designer           |

| Routability of block terminals (pin placement, access) | Layout<br>GDSII<br>OA abstract<br>LEF | Automated<br>(script)           | IP designer<br>+ imec |

| Library cell template and abutment                     | Layout<br>GDSII<br>OA abstract<br>LEF | Automated<br>(script)           | imec                  |

| Mask layer numbers                                     | GDSII                                 | Automated<br>(script)           | IP designer<br>+ imec |

| Library/IP cell list completeness                      | all                                   | Automated<br>(script)           | IP designer<br>+ imec |

| Characterization data value consistency                | Liberty                               | Automated<br>(Library Compiler) | IP designer           |

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| DELIVERABLE: | D1.3 - Interface Standards       |

|--------------|----------------------------------|

| Date:        | & IP Usage Definition 23/04/2020 |

| ISSUE: | 002 |

|--------|-----|

|--------|-----|

Page: 16/27

| Check                             | Views            | Method<br>(Tool)                | Responsible           |

|-----------------------------------|------------------|---------------------------------|-----------------------|

| Liberty file syntax and semantics | Liberty          | Automated<br>(Library Compiler) | IP designer<br>+ imec |

| HDL file syntax                   | Verilog<br>VITAL | Automated<br>(Modelsim)         | IP designer<br>+ imec |

| IBIS syntax                       | IBIS             | Automated<br>(ibis_chk)         | imec                  |

#### **CROSS-VIEW CHECKS** 3.2.

Requirement IS-DDVA-19:

Design tools require matching information across different views. Several consistency checks between views must be performed by IP providers and imec top-level designers.

[vmethod: Analysys]

| Check                                 | Cross Views                                                                                                                                                       | Method<br>(Tool)           | Responsible           |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|

| All views present                     | all                                                                                                                                                               | Automated<br>(script)      | IP designer<br>+ imec |

| All cells present                     | all                                                                                                                                                               | Automated<br>(script)      | IP designer<br>+ imec |

| Matching pin order                    | CDL vs. OA symbol<br>CDL vs. PEX netlist<br>CDL vs. PEX netlist<br>CDL vs. encrypted PEX netlist<br>CDL vs. black-box CDL<br>CDL vs. Verilog<br>CDL vs. Verilog-A | Automated<br>(script)      | IP designer           |

| Matching pin name, type and direction | all                                                                                                                                                               | Automated<br>(script)      | IP designer<br>+ imec |

| Layout versus Schematic (LVS)         | GDSII vs. CDL<br>OA abstract vs. black-box CDL                                                                                                                    | Automated<br>(Calibre/PVS) | IP designer<br>+ imec |

| Matching SDF annotation               | Liberty vs. Verilog                                                                                                                                               | Automated<br>(Liberate)    | IP designer<br>+ imec |

ເກາec

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| DELIVERABLE | -       | D1.3 - Interface Standards<br>& IP Usage Definition |  |

|-------------|---------|-----------------------------------------------------|--|

| DATE:       | 23/04/2 | 2020                                                |  |

| ISSUE:      | 002     | Page: 17/27                                         |  |

## 4. **DESIGN FLOWS [DFLW]**

Requirement IS-DFLW-20 :

This section describes the use of distributed IP views in analog-on-top and digital-on-top methodologies for ASIC design. As well, the digital-on-top flow can be used to implement digital circuits for complex mixed-signal IP blocks which are designed using the analog-on-top methodology.

[vmethod: Analysys]

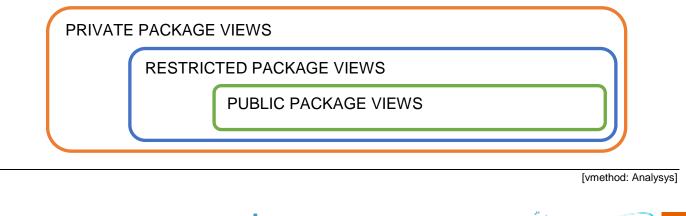

### 4.1. ANALOG-ON-TOP FLOW

Requirement IS-DFLW-21 :

Analog-on-top methodology employs a schematic-driven flow to implement analog-centric designs with small amounts of digital logic. In this flow, designers must place all blocks in the design and route all signals by hand.

This flow is preferred for analog and mixed-signal IP design. As well, it may be used for toplevel chip design mainly in the case of purely analog systems.

Tools for analog-on-top design include design tools (e.g. Cadence Virtuoso), physical verification tools (e.g. Cadence PVS) and functional verification tools (e.g. Cadence Spectre).

Analog-on-top design may require the following views:

- OA symbol/spectre/auCdl/auLVS

- GDSII or OA layout or black-box OA abstract

- CDL netlist or OA schematic or black-box CDL netlist

- PEX netlist or encrypted PEX netlist

[vmethod: Analysys]

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| Deliverable:<br>Date: |     | erface Standards<br>le Definition<br>0 |

|-----------------------|-----|----------------------------------------|

| ISSUE:                | 002 | Page: 18/27                            |

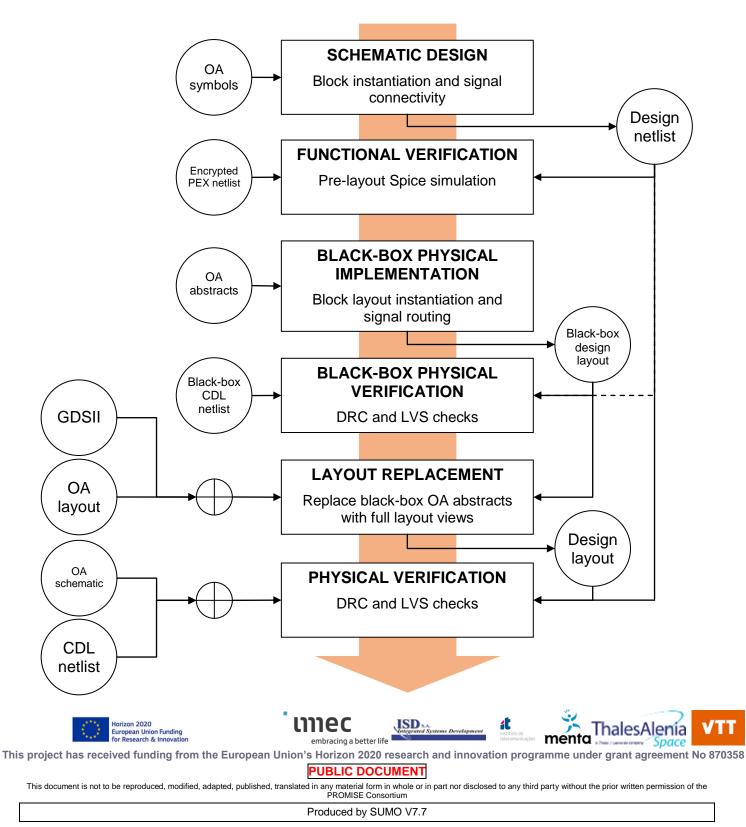

#### 4.1.1. **Analog Design Flow Using Full Design Views**

A typical analog design flow using full design views is depicted in the diagram below.

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

|         | DELIVERABLE: | -       | Interface Standards sage Definition |

|---------|--------------|---------|-------------------------------------|

| PROMISE | DATE:        | 23/04/2 | •                                   |

|         | ISSUE:       | 002     | Page: 19/27                         |

#### 4.1.2. Analog Design Flow Using Black-Box Design Views

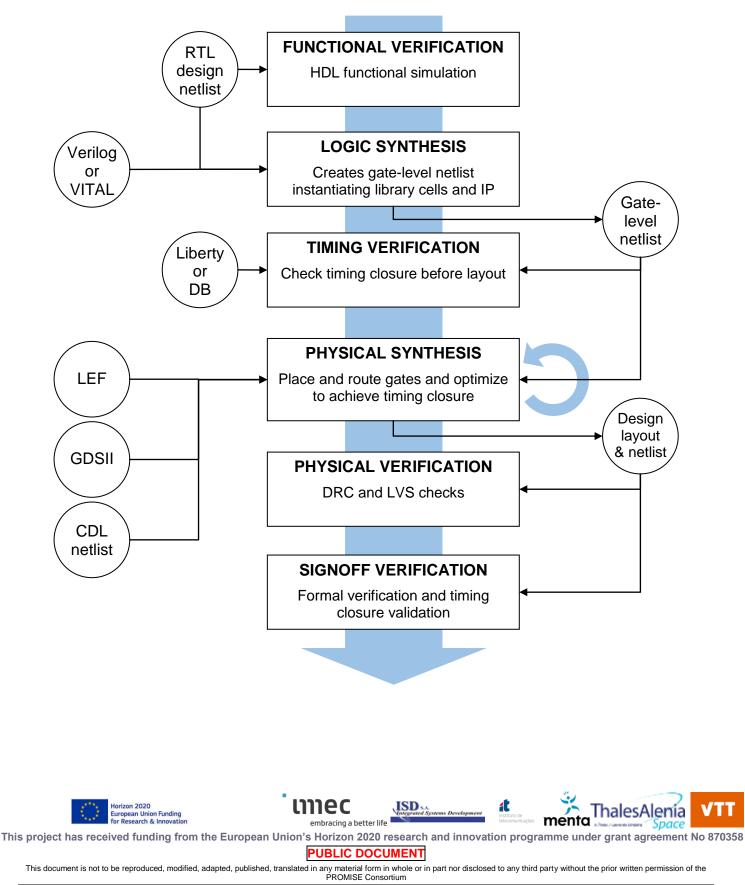

In case GDSII/OA layout and CDL/OA schematic views are not available, it is possible to implement designs using black-box views. In this case, additional actions are required to obtain final tape-out layout by replacing black-box views with full views, as depicted in the diagram below.

| DELIVERABLE: | D1.3 - Interface Standards<br>& IP Usage Definition |             |

|--------------|-----------------------------------------------------|-------------|

| DATE:        | 23/04/2                                             | •           |

| ISSUE:       | 002                                                 | Page: 20/27 |

### 4.2. DIGITAL-ON-TOP FLOW

Requirement IS-DFLW-22 :

Digital-on-top methodology uses a high-level netlist-driven flow to implement designs with large amounts of digital logic. In such flow, high levels abstraction and tool automation are employed to handle complex design and verification tasks which require additional library views.

Tools for digital-on-top design include functional verification tools (e.g. Mentor Modelsim), physical design tools (e.g. Cadence Innovus) and physical verification tools (e.g. Cadence PVS).

Digital-on-top design requires at least the following views:

- GDSII

- LEF

- CDL netlist

- Liberty file or Synopsys DB library

- Verilog or VITAL library models

In addition, digital flows require design views such as functional high-level RTL design description (Verilog or VITAL) and constraint specification (SDC).

[vmethod: Analysys]

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| DELIVERABLE | -       | D1.3 - Interface Standards<br>& IP Usage Definition |  |

|-------------|---------|-----------------------------------------------------|--|

| DATE:       | 23/04/2 | 0                                                   |  |

| ISSUE:      | 002     | Page: 21/27                                         |  |

A basic digital-on-top flow is depicted in the diagram below.

| DELIVERABLE: | D1.3 - Interface Standards<br>& IP Usage Definition |             |

|--------------|-----------------------------------------------------|-------------|

| DATE:        | 23/04/2                                             |             |

| ISSUE:       | 002                                                 | Page: 22/27 |

#### 4.3. **MIXED-SIGNAL DESIGN**

Requirement IS-DFLW-23 :

Analog and digital flows can be combined in the design of complex mixed-signal applications.

Although analog-on-top methodology is mainly used to design IP blocks for later use in digitalon-top flows, designers implementing complex IPs with large digital functions (e.g ADC) can also make use of the digital flows to design digital parts of such blocks in an automated way. Digital-on-top outputs (e.g GDSII, CDL netlist) can then be imported in analog-on-top flows to be combined with other circuit components.

[vmethod: Analysys]

#### 5. **COMPLIANCE MATRIX**

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| DELIVERABLE: | D1.3 - Interface Standards       |

|--------------|----------------------------------|

| DATE:        | & IP Usage Definition 23/04/2020 |

**ISSUE:** 001

Page: 23/27

| Reference  | Description                                                                                                                                                                                                                                                                                                                                                                                                                               | Compliance | Verification<br>method |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|

| IS-IPDE-01 | IP deliverables refer to the set of library or IP views provided by any partner design house.                                                                                                                                                                                                                                                                                                                                             |            |                        |

| IS-IPDE-02 | IPdeliverabledatawillbedistributedintarballcompressedpackagefilescontainingviews anddocumentationarrangedinapredefineddirectorystructure.                                                                                                                                                                                                                                                                                                 |            |                        |

| IS-IPDE-03 | Each deliverable package file will combine data for a single IP.                                                                                                                                                                                                                                                                                                                                                                          |            |                        |

| IS-IPDE-04 | Each IP will have its own serial version tag number indicated in package file name and package directory structure.                                                                                                                                                                                                                                                                                                                       |            |                        |

| IS-IPDE-05 | <ul> <li>IP views are classified in different distribution categories:</li> <li>Public: views distributed without restriction to anyone.</li> <li>Restricted: views suitable for distribution to any user under NDA.</li> <li>Private: sensitive proprietary data only disclosed to selected partners under special NDA.</li> <li>Packages variants will be created for every IP to combine views for each distribution scope.</li> </ul> |            |                        |

| IS-IPDE-06 | The table below indicates a minimum recommended IP views that should be distributed in order to support digital and analog design flows. Certain views apply only to selected types of IP blocks, as indicated in the table.                                                                                                                                                                                                              |            |                        |

| IS-IPDE-07 | ThislistisnotexhaustiveasadditionalviewsmayberequiredforcertainIPs.                                                                                                                                                                                                                                                                                                                                                                       |            |                        |

| IS-IPDE-09 | All package views will be arranged in a standardized directory structure as shown below. File names and extensions for each view are indicated in this template.                                                                                                                                                                                                                                                                          |            |                        |

| IS-IPDE-10 | Additional views not foreseen in this document should be placed in separate subdirectories at the same level as other views, under Back_End, Front_End or                                                                                                                                                                                                                                                                                 |            |                        |

unec ISD SA embracing a better life

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

institut telecon

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

ms Develonment

DELIVERABLE:D1.3 - Interface Standards<br/>& IP Usage DefinitionDATE:23/04/2020

001

ISSUE:

Page: 24/27

| Reference  | Description                                                                                                                                                                                                                                              | Compliance | Verification<br>method |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|

|            | Documentation directories, depending on which design phase they are mainly used.                                                                                                                                                                         |            |                        |

| IS-IPDE-11 | IP version tagg intends to enable full traceability of data and versions used in designs.                                                                                                                                                                |            |                        |

| IS-IPDE-12 | IP version numbers should comply to the format Vx_y_z, where x integer indicates a major update, y integer indicates a minor update, and z indicates a version number relevant internally to the IP provider. Example: DARE180XH_CORE_V2.1.349.          |            |                        |

| IS-IPDE-13 | Versionnumbersmustbeincludedinthepackagenameanditsdirectorystructure, asshow ninparagraph 2.3.                                                                                                                                                           |            |                        |

| IS-IPDE-14 | IP version and ownership information should be placed in all documentation, GDSII and text-format views. In the case of text files, header comments can be used, as shown in the example below. IP providers are free to use their own formatting style. |            |                        |

| IS-IPDE-15 | In the case of GDSII, tags should be added and encoded in accordance with the VSIA's IP tagging standard (RD1).                                                                                                                                          |            |                        |

| IS-DDVA-16 | IP views must be validated upon release to users by its design house. Certain sanity checks will also be performed at imec upon starting top-level designs using deliverables from IP providers.                                                         |            |                        |

| IS-DDVA-17 | A minimum required set of verification procedures is defined in this section.                                                                                                                                                                            |            |                        |

| IS-DDVA-18 | Several verification procedures must be applied on individual IP views.                                                                                                                                                                                  |            |                        |

| IS-DDVA-19 | Design tools require matching information across different views. Several consistency checks between views must be performed by IP providers and imec top-level designers.                                                                               |            |                        |

| IS-DFLW-20 | This section describes the use of distributed IP views in analog-on-top and digital-                                                                                                                                                                     |            |                        |

embracing a better life

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

| DELIVERABLE: | D1.3 - Interface Standards |

|--------------|----------------------------|

|              | & IP Usage Definition      |

| DATE:        | 23/04/2020                 |

001

ISSUE:

Page: 25/27

| Reference  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Compliance | Verification<br>method |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|

|            | on-top methodologies for ASIC design. As well, the digital-on-top flow can be used to implement digital circuits for complex mixed-signal IP blocks which are designed using the analog-on-top methodology.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                        |

| IS-DFLW-21 | <ul> <li>Analog-on-top methodology employs a schematic-driven flow to implement analog-centric designs with small amounts of digital logic. In this flow, designers must place all blocks in the design and route all signals by hand.</li> <li>This flow is preferred for analog and mixed-signal IP design. As well, it may be used for top-level chip design mainly in the case of purely analog systems.</li> <li>Tools for analog-on-top design include design tools (e.g. Cadence Virtuoso), physical verification tools (e.g. Cadence PVS) and functional verification tools (e.g. Cadence Spectre).</li> <li>Analog-on-top design may require the following views:</li> <li>OA symbol/spectre/auCdl/auLVS</li> <li>GDSII or OA layout or black-box OA abstract</li> <li>CDL netlist or OA schematic or black-box CDL netlist</li> <li>PEX netlist or encrypted PEX netlist</li> </ul> |            |                        |

| IS-DFLW-22 | <ul> <li>Digital-on-top methodology uses a high-level netlist-driven flow to implement designs with large amounts of digital logic. In such flow, high levels abstraction and tool automation are employed to handle complex design and verification tasks which require additional library views.</li> <li>Tools for digital-on-top design include functional verification tools (e.g. Mentor Modelsim), physical design tools (e.g. Cadence Innovus) and physical verification tools (e.g. Cadence PVS).</li> <li>Digital-on-top design requires at least the following views:</li> </ul>                                                                                                                                                                                                                                                                                                   |            |                        |

embracing a better life

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

ISD SA

PUBLIC DOCUMENT

institut.

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

ms Develonment

DELIVERABLE:D1.3 - Interface Standards<br/>& IP Usage DefinitionDATE:23/04/2020

001

ISSUE:

Page: 26/27

| Reference  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Compliance | Verification<br>method |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|

|            | GDSII<br>LEF<br>CDL netlist<br>Liberty file or Synopsys DB library<br>Verilog or VITAL library models<br>In addition, digital flows require design views such as functional high-level RTL                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                        |

| IS-DFLW-23 | <ul> <li>design description (Verilog or VITAL) and constraint specification (SDC).</li> <li>Analog and digital flows can be combined in the design of complex mixed-signal applications.</li> <li>Although analog-on-top methodology is mainly used to design IP blocks for later use in digital-on-top flows, designers implementing complex IPs with large digital functions (e.g ADC) can also make use of the digital flows to design digital parts of such blocks in an automated way. Digital-on-top outputs (e.g GDSII, CDL netlist) can then be imported in analog-on-top flows to be combined with other circuit components.</li> </ul> |            |                        |

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium

|         | DELIVERABLE: | D1.3 - Interface Standards<br>& IP Usage Definition<br>23/04/2020 |             |

|---------|--------------|-------------------------------------------------------------------|-------------|

| PROMISE | DATE:        |                                                                   |             |

|         | ISSUE:       | 001                                                               | Page: 27/27 |

## **END OF DOCUMENT**

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 870358

PUBLIC DOCUMENT

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of the PROMISE Consortium